디지털을 배우고 익히지 않으신 예전 아날로그 세대이신 분들께는 공감하기 어려운 이야기일 수 있겠지만

본업으로 두가지 다 해본 입장에서 볼 때, 난이도는 분명 아날로그가 훨씬 더 어렵습니다.

다만 디지털의 경우는 다시 소프트웨어라는 넘과 얽히게 되는데, 이것 때문에 어렵게 느껴질 수는 있지만

소프트웨어와 경계선이 모호한 영역인 아키텍쳐분야를 제외하면 디지털은 그리 어려울 것이 없습니다.

사실, 아키텍쳐라는 분야도 다양한 영역의 비교적 얕은 지식을 망라해서 정리해야 하는 경우가 많아서

난이도가 높다기 보다는 깊고 좁게 공부하면 접근하기 어려운 분야이기 때문에 어렵게 느껴지는 경우가

대부분이기도 하구요.

특히나 요즘 디지털회로는 무조건 CMOS입니다. 뭐 이것저것 따질 것 없이 N-MOS니 TTL이니, ECL이니

이런것은 이미 사장되었다고 봐도 무방합니다. 디지털 로직을 구성하는 기본 소자가 MOS-FET 2종으로

모든 것이 해결된다고 보시면 됩니다.

마이크로전자회로나 기타 전자회로 책에서도 보시면 리니어나 아날로그영역에 비해 디지털 로직은

훨씬 양도 적고, 단순하게 나옵니다. 사실상 그것이 끝입니다. 이런 기본 로직이 다시 모여서 시스템을

구성하는 것인데, 시스템은 어느새 아키텍쳐의 영역이 되어 버립니다.

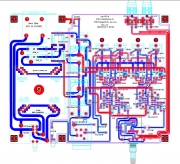

여튼, CMOS는 P-MOS와 N-MOS소자를 이용해서 pull-up stage와 pull-down stage로 구분되어 회로가

구성되어 합쳐지게 되는데, Inverter, NAND, NOR, Transition Logic 이렇게 4종으로 끝난다고 보시면

됩니다...^^

디지털회로의 트러블슈팅시에 맨 먼저 하는 것이 오류가 로직오류인지 회로 오류인지 판단해야 합니다.

초기에 이걸 잘못하면 완전 삽질이 될 수 있습니다만 이것만 잘 구분해도 절반은 성공입니다. 로직은

요즘 시뮬레이션이 워낙 좋아져서 대부분 이걸로 다 해결이 됩니다. 회로의 트러블도 아주 단순합니다.

주로 트러블이 발생하는 것이 로직의 출력 하나를 여러 로직의 입력으로 쓰게 되는 경우 한번에 너무

많이 물려 버리면 fan-out문제가 발생합니다. 그리고 주로 대규모의 IC류를 주로 쓰다보니 안쓰는

핀이 발생하기도 하는데, CMOS에서 철칙이 절대로 입력핀을 floating상태로 두면 안됩니다. high이든

low이든 한쪽에 확실히 물려야 합니다. 이것은 마이크로전자회로같은 책에서 CMOS Inverter를 설명해

놓은 부분을 잘 보시면 중간의 애매한 입력전압이 걸리면 pull-up stage와 pull-down stage가 동시에

열리게 되는데, 이 상태로 지속되면 예전엔 소자가 손상되는 경우도 있었지만 요즘은 그렇게까지

가지는 않지만 게이트 하나당 0.5~1mA정도의 지속적인 leackage current가 발생하게 됩니다. 문제는

이렇게 중간 전압 정도가 걸리는 게이트의 출력도 애매하게 걸릴 수 있어서 상황에 따라서는 여러

게이트가 한번에 leackage가 걸릴 수도 있습니다. (확률은 많이 낮지만)

좌우지간, 디지털회로는 이런 몇가지 트러블 시나리오만 미리 예방해 주면 아주 쉽습니다. 그냥 뭐

날로 먹는다고 할 수도 있죠...^^

공고 전기회로 교과서를 질렀습니다.^^

공고 전기회로 교과서를 질렀습니다.^^